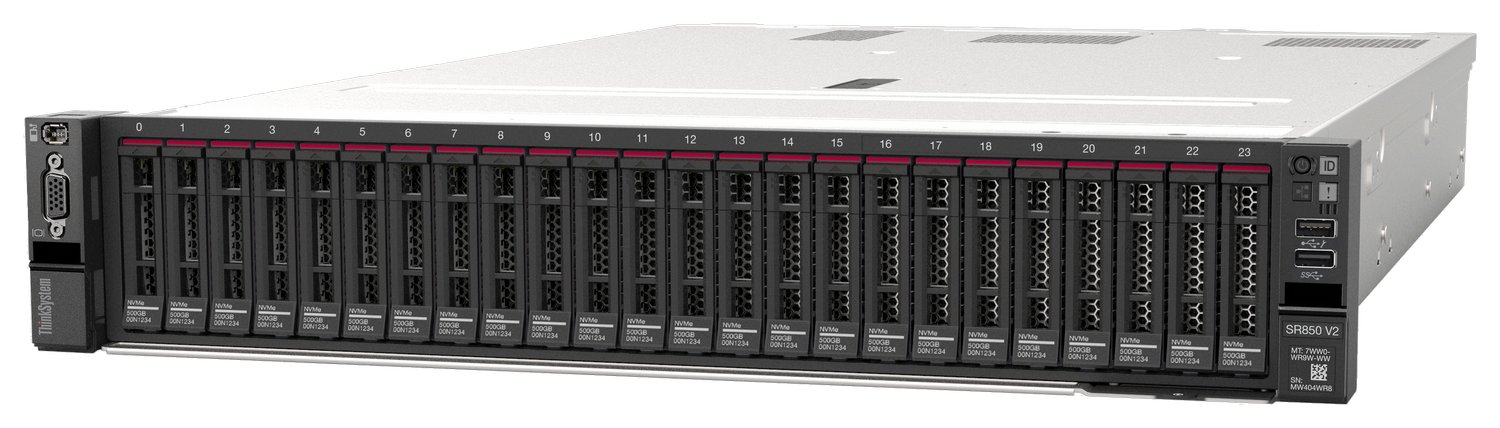

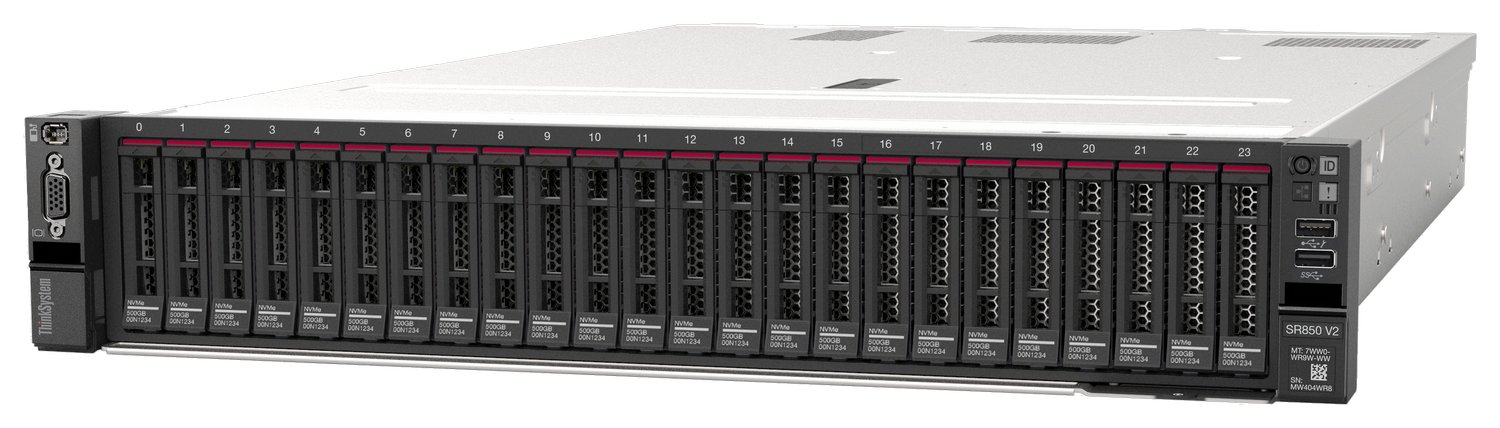

ThinkSystem SR850 V2 (7D31, 7D32)

Lenovo ThinkSystem SR850 V2 server (machine type: 7D31, 7D32) is a 2U rack server designed for high-volume network transaction processing. This high-performance, multi-core server is ideally suited for networking environments that require superior processor performance, input/output (I/O) flexibility, and high manageability.

Figure 1. ThinkSystem SR850 V2

- Resources and downloads

Download product document/driver/firmware resources and discover handy channels for support. - Server package contents

When you receive your server, verify that the shipment contains everything that you expected to receive. - Features

Performance, ease of use, reliability, and expansion capabilities were key considerations in the design of your server. These design features make it possible for you to customize the system hardware to meet your needs today and provide flexible expansion capabilities for the future. - Specifications

The following information is a summary of the features and specifications of the server. Depending on the model, some features might not be available, or some specifications might not apply. - Management options

The XClarity portfolio and other system management options described in this section are available to help you manage the servers more conveniently and efficiently. - Server components

This section contains information about each of the components associated with the server. - Internal cable routing

See this section to do cable routing for specific components. - Server hardware setup

To set up the server, install any options that have been purchased, cable the server, configure and update the firmware, and install the operating system. - System configuration

Complete these procedures to configure your system. - Hardware replacement procedures

This section provides installation and removal procedures for all serviceable system components. Each component replacement procedure references any tasks that need to be performed to gain access to the component being replaced. - Problem determination

Use the information in this section to isolate and resolve issues that you might encounter while using your server. - Messages

When attempting to resolve issues with your server, the best practice is to begin with the event log of the application that is managing the server. - Tech Tips

Lenovo continually updates the support website with the latest tips and techniques that you can use to solve issues that your server might encounter. These Tech Tips (also called retain tips or service bulletins) provide procedures to work around issues or solve problems related to the operation of your server. - Security advisories

Lenovo is committed to developing products and services that adhere to the highest security standards in order to protect our customers and their data. When potential vulnerabilities are reported, it is the responsibility of the Lenovo Product Security Incident Response Team (PSIRT) to investigate and provide information to our customers so they may put mitigation plans in place as we work toward providing solutions. - Hardware disassembling for recycle

Follow the instructions in this section to recycle components with compliance with local laws or regulations. - Getting help and technical assistance

If you need help, service, or technical assistance or just want more information about Lenovo products, you will find a wide variety of sources available from Lenovo to assist you.

Give documentation feedback