Règles et ordre d’installation d’un module de mémoire

Les modules de mémoire doivent être installés dans un ordre spécifique, selon la configuration de mémoire que vous implémentez sur le nœud.

Pour plus d’informations sur les types de modules de mémoire pris en charge par le serveur, voir la section Mémoire dans Spécifications techniques

Mode mémoire indépendant

Des informations sur l’optimisation des performances mémoire et la configuration de la mémoire sont disponibles sur le site Lenovo Press à l’adresse suivante :

En outre, vous pouvez utiliser un configurateur de mémoire, qui est disponible sur le site suivant :

Lenovo Enterprise Solutions Configurator (configurations de mémoire)

Vous trouverez ci-dessous des informations spécifiques concernant l’ordre d’installation requis des modules de mémoire dans votre solution en fonction de la configuration système et du mode mémoire que vous mettez en œuvre.

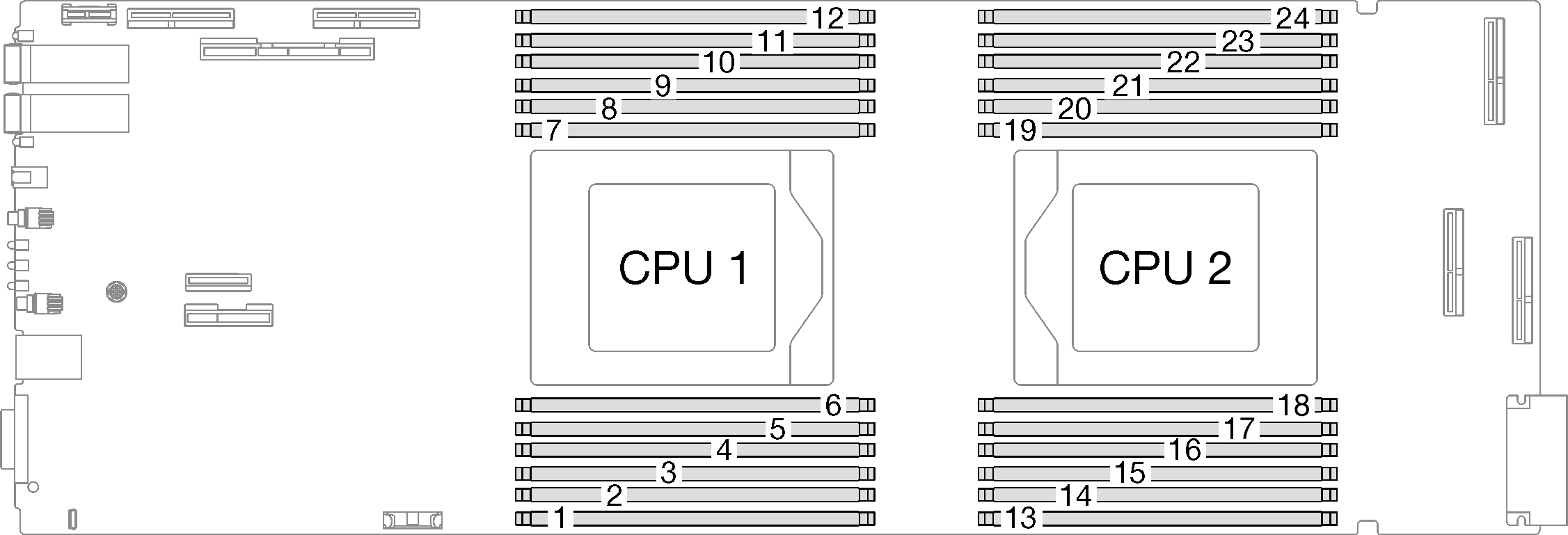

Disposition des modules de mémoire et des processeurs

Le tableau de configuration des canaux de mémoire ci-dessous montre les relations entre les processeurs, les canaux de mémoire et les numéros des emplacements des modules de mémoire.

| UC | UC 1 | |||||||||||

| Canal | F | E | D | C | B | A | G | H | I | J | K | L |

| Numéro d’emplacement DIMM | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 |

| UC | UC 2 | |||||||||||

| Canal | L | K | J | I | H | G | A | B | C | D | E | F |

| Numéro d’emplacement DIMM | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 |

Ordre d’installation des modules DIMM DRAM pour le mode indépendant

Le mélange de DIMM de capacités, types et marques différents n’est pas autorisé. Tous les modules DIMM installés dans le système doivent être identiques.

Mode mémoire indépendant

8 modules DIMM par processeur, soit un total de 16 modules DIMM par nœud

12 modules DIMM par processeur, soit un total de 24 modules DIMM par nœud

Séquence de remplissage de la mémoire en mode indépendant pour 8 DIMM par processeur, pour un total de 16 DIMM par nœud

| Processeur | Processeur 1 | |||||||||||

| Emplacements DIMM | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 |

| 8 Barrettes DIMM | 2 | 4 | 5 | 6 | 7 | 8 | 9 | 11 | ||||

| Processeur | Processeur 2 | |||||||||||

| Emplacements DIMM | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 |

| 8 Barrettes DIMM | 14 | 16 | 17 | 18 | 19 | 20 | 21 | 23 | ||||

Séquence de remplissage de la mémoire en mode indépendant pour 12 DIMM par processeur, pour un total de 24 DIMM par nœud

| Processeur | Processeur 1 | |||||||||||

| Emplacements DIMM | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 |

| 12 Barrettes DIMM | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 |

| Processeur | Processeur 2 | |||||||||||

| Emplacements DIMM | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 |

| 12 Barrettes DIMM | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 |