Règles d'installation de barrette DIMM

Les barrettes DIMM doivent être installées dans un ordre spécifique, selon la configuration de mémoire que vous mettez en place sur votre serveur.

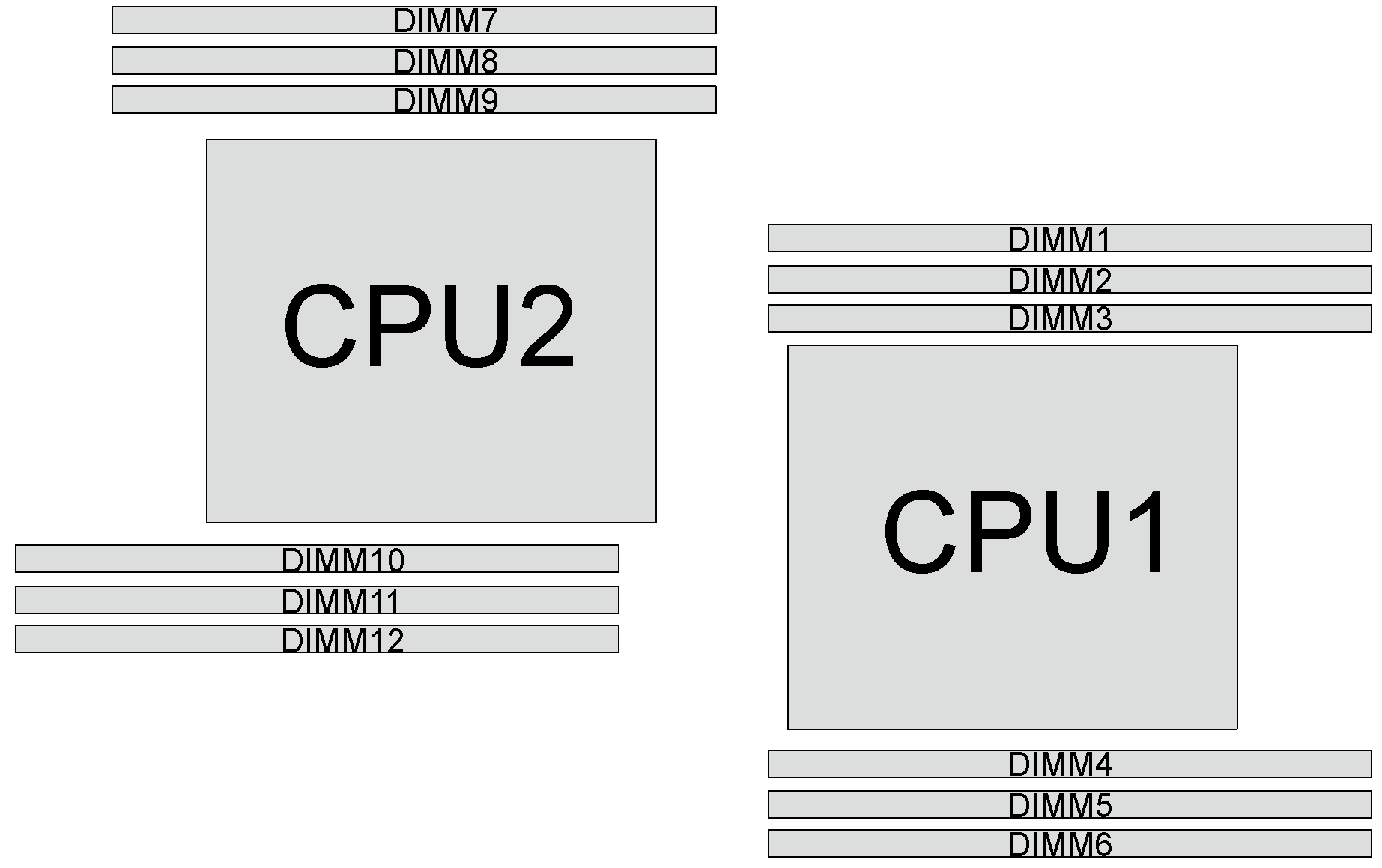

Votre serveur est équipé de 12 emplacements pour barrettes DIMM. Il prend en charge jusqu'à 6 barrettes DIMM lorsqu'un processeur est installé et jusqu'à 12 barrettes DIMM lorsque deux processeurs sont installés. Il comprend les dispositifs suivants :

Pour les processeurs Intel Xeon SP Gen 1

Minimum : 8 Go (un processeur et une barrette RDIMM 8 Go installés)

Maximum :

384 Go à l’aide de barrettes RDIMM (deux processeurs et douze barrettes RDIMM 32 Go (RDIMM) installés)

768 Go à l’aide de barrettes LRDIMM (deux processeurs et douze barrettes LRDIMM 64 Go installés)

Type :

TruDDR4 2666, à un rang/à deux rangs, RDIMM 8 Go/16 Go/32 Go

TruDDR4 2666, à quatre rangs, 64 Go barrettes LRDIMM

Pour les processeurs Intel Xeon SP Gen 2

Minimum : 8 Go (un processeur et une barrette RDIMM 8 Go installés)

Maximum : 768 Go (deux processeurs et douze barrettes RDIMM 64 Go installés)

Type :

TruDDR4 2666, à un rang/à deux rangs, RDIMM 16 Go/32 Go

TruDDR4 2933, à un rang/à deux rangs, RDIMM 8 Go/16 Go/32 Go/64 Go

Pour connaître la liste des options DIMM prises en charge, voir : Site Web Lenovo ServerProven

DDR4 RDIMM avec un code correcteur d'erreurs (ECC)

DDR4 LRDIMM (non pris en charge pour les processeurs Intel Xeon SP Gen 2) avec la technologie ECC

Mode indépendant

Le mode indépendant offre de hautes performances mémoire. Vous pouvez peupler tous les canaux sans conditions de correspondance. Les canaux individuels peuvent s'exécuter à différents moments sur les barrettes DIMM, mais tous les canaux doivent s'exécuter à la même fréquence d'interface.

Toutes les barrettes DIMM à installer doivent être du même type.

Si vous installez des barrettes DIMM de même rang et de différentes capacités, installez d'abord la barrette DIMM ayant la capacité la plus élevée.

Le tableau ci-après indique la séquence de peuplement des barrettes DIMM pour le mode indépendant lorsqu'un processeur (CPU1) est installé.

| Total | Processeur 1 | Total | ||||||

|---|---|---|---|---|---|---|---|---|

| Des barrettes DIMM | 1 | 2 | 3 | 4 | 5 | 6 | Des barrettes DIMM | |

| 1 | 3 | 1 | ||||||

| 2 | 3 | 4 | 2 | |||||

| 3 | 2 | 3 | 4 | 3 | ||||

| 4 | 2 | 3 | 4 | 5 | 4 | |||

| 5 | 1 | 2 | 3 | 4 | 5 | 5 | ||

| 6 | 1 | 2 | 3 | 4 | 5 | 6 | 6 | |

Le tableau ci-après indique la séquence de peuplement des barrettes DIMM pour le mode indépendant lorsque deux processeurs (CPU1 et CPU2) sont installés.

S'il y a trois barrettes DIMM identiques à installer pour CPU1, et que ces trois barrettes DIMM portent le même numéro de référence Lenovo, installez les trois barrette DIMM dans les emplacements 1, 2 et 3.

S'il y a trois barrettes DIMM identiques à installer pour CPU2, et que ces trois barrettes DIMM portent le même numéro de référence Lenovo, installez les trois barrette DIMM dans les emplacements 10, 11 et 12.

| Total | Processeur 1 | Processeur 2 | Total | |||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Des barrettes DIMM | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | Des barrettes DIMM | |||

| 2 | 3 | 10 | 2 | |||||||||||||

| 3 | 3 | 4 | 10 | 3 | ||||||||||||

| 4 | 3 | 4 | 9 | 10 | 4 | |||||||||||

| 5 | 2 | 3 | 4 | 9 | 10 | 5 | ||||||||||

| 6 | 2 | 3 | 4 | 9 | 10 | 11 | 6 | |||||||||

| 7 | 2 | 3 | 4 | 5 | 9 | 10 | 11 | 7 | ||||||||

| 8 | 2 | 3 | 4 | 5 | 8 | 9 | 10 | 11 | 8 | |||||||

| 9 | 1 | 2 | 3 | 4 | 5 | 8 | 9 | 10 | 11 | 9 | ||||||

| 10 | 1 | 2 | 3 | 4 | 5 | 8 | 9 | 10 | 11 | 12 | 10 | |||||

| 11 | 1 | 2 | 3 | 4 | 5 | 6 | 8 | 9 | 10 | 11 | 12 | 11 | ||||

| 12 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 12 | |||

Mode de mise en miroir

En mode de mise en miroir, la taille et l'architecture de chacune des barrettes DIMM d'une paire doivent être identiques. Les canaux sont regroupés par paires et chaque canal reçoit les mêmes données. Un canal est utilisé comme sauvegarde de l'autre, ce qui permet la redondance.

Le tableau ci-après indique la séquence de peuplement des barrettes DIMM pour le mode de mise en miroir mémoire lorsqu'un seul processeur (CPU1) est installé.

| Total | Processeur 1 | Total | ||||||

|---|---|---|---|---|---|---|---|---|

| Des barrettes DIMM | 1 | 2 | 3 | 4 | 5 | 6 | Des barrettes DIMM | |

| 2 | 2 | 3 | 2 | |||||

| 3 | 1 | 2 | 3 | 3 | ||||

| 4 | 2 | 3 | 4 | 5 | 4 | |||

| 6 | 1 | 2 | 3 | 4 | 5 | 6 | 6 | |

Le tableau ci-après indique la séquence de peuplement des barrettes DIMM pour le mode de mise en miroir mémoire lorsque deux processeurs (CPU1 et CPU2) sont installés.

| Total | Processeur 1 | Processeur 2 | Total | |||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Des barrettes DIMM | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | Des barrettes DIMM | |||

| 4 | 2 | 3 | 10 | 11 | 4 | |||||||||||

| 5 | 1 | 2 | 3 | 10 | 11 | 5 | ||||||||||

| 6 | 1 | 2 | 3 | 10 | 11 | 12 | 6 | |||||||||

| 8 | 2 | 3 | 4 | 5 | 8 | 9 | 10 | 11 | 8 | |||||||

| 9 | 1 | 2 | 3 | 4 | 5 | 6 | 10 | 11 | 12 | 9 | ||||||

| 10 | 1 | 2 | 3 | 4 | 5 | 6 | 8 | 9 | 10 | 11 | 10 | |||||

| 12 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 12 | |||

Mode de mise en réserve mémoire par rang

En mode de mise en réserve mémoire par rang, un rang de barrettes DIMM sert de rang de secours pour les autres rangs d'un même canal. Le rang de secours n'est pas disponible pour la mémoire système.

Toutes les barrettes DIMM à installer doivent être du même type, avec la même capacité, la même fréquence, la même tension et le même rang.

Si le rang des barrettes DIMM installées est un rang, le mode de mise en réserve mémoire par rang n'est pas pris en charge. Si le rang des barrettes DIMM est supérieur à un rang, suivez les règles d'installation indiquées dans les tableaux suivants.

Le tableau ci-après indique la séquence de peuplement des barrettes DIMM pour le mode de mise en réserve mémoire par rang lorsqu'un seul processeur (CPU1) est installé.

| Total | Processeur 1 | Total | ||||||

|---|---|---|---|---|---|---|---|---|

| Des barrettes DIMM | 1 | 2 | 3 | 4 | 5 | 6 | Des barrettes DIMM | |

| 1 | 3 | 1 | ||||||

| 2 | 3 | 4 | 2 | |||||

| 3 | 2 | 3 | 4 | 3 | ||||

| 4 | 2 | 3 | 4 | 5 | 4 | |||

| 5 | 1 | 2 | 3 | 4 | 5 | 5 | ||

| 6 | 1 | 2 | 3 | 4 | 5 | 6 | 6 | |

Le tableau ci-après indique la séquence de peuplement des barrettes DIMM pour le mode de mise en réserve mémoire par rang lorsque deux processeurs (CPU1 et CPU2) sont installés.

| Total | Processeur 1 | Processeur 2 | Total | |||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Des barrettes DIMM | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | Des barrettes DIMM | |||

| 2 | 3 | 10 | 2 | |||||||||||||

| 3 | 3 | 4 | 10 | 3 | ||||||||||||

| 4 | 3 | 4 | 9 | 10 | 4 | |||||||||||

| 5 | 2 | 3 | 4 | 9 | 10 | 5 | ||||||||||

| 6 | 2 | 3 | 4 | 9 | 10 | 11 | 6 | |||||||||

| 7 | 2 | 3 | 4 | 5 | 9 | 10 | 11 | 7 | ||||||||

| 8 | 2 | 3 | 4 | 5 | 8 | 9 | 10 | 11 | 8 | |||||||

| 9 | 1 | 2 | 3 | 4 | 5 | 8 | 9 | 10 | 11 | 9 | ||||||

| 10 | 1 | 2 | 3 | 4 | 5 | 8 | 9 | 10 | 11 | 12 | 10 | |||||

| 11 | 1 | 2 | 3 | 4 | 5 | 6 | 8 | 9 | 10 | 11 | 12 | 11 | ||||

| 12 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 12 | |||