Speicherspiegelung

Der Speicherspiegelungsmodus bietet eine vollständige Speicherredundanz, während gleichzeitig die gesamte Systemspeicherkapazität um die Hälfte verringert wird. Speicherkanäle werden in Paaren gruppiert, wobei jeder Kanal dieselben Daten empfängt. Wenn ein Fehler auftritt, schaltet der Speichercontroller von den DIMMs auf dem primären Kanal auf die DIMMs auf dem Ausweichkanal. Die DIMM-Installationsreihenfolge für die Speicherspiegelung variiert basierend auf der Anzahl an Prozessoren und DIMMs, die im Rechenknoten installiert sind.

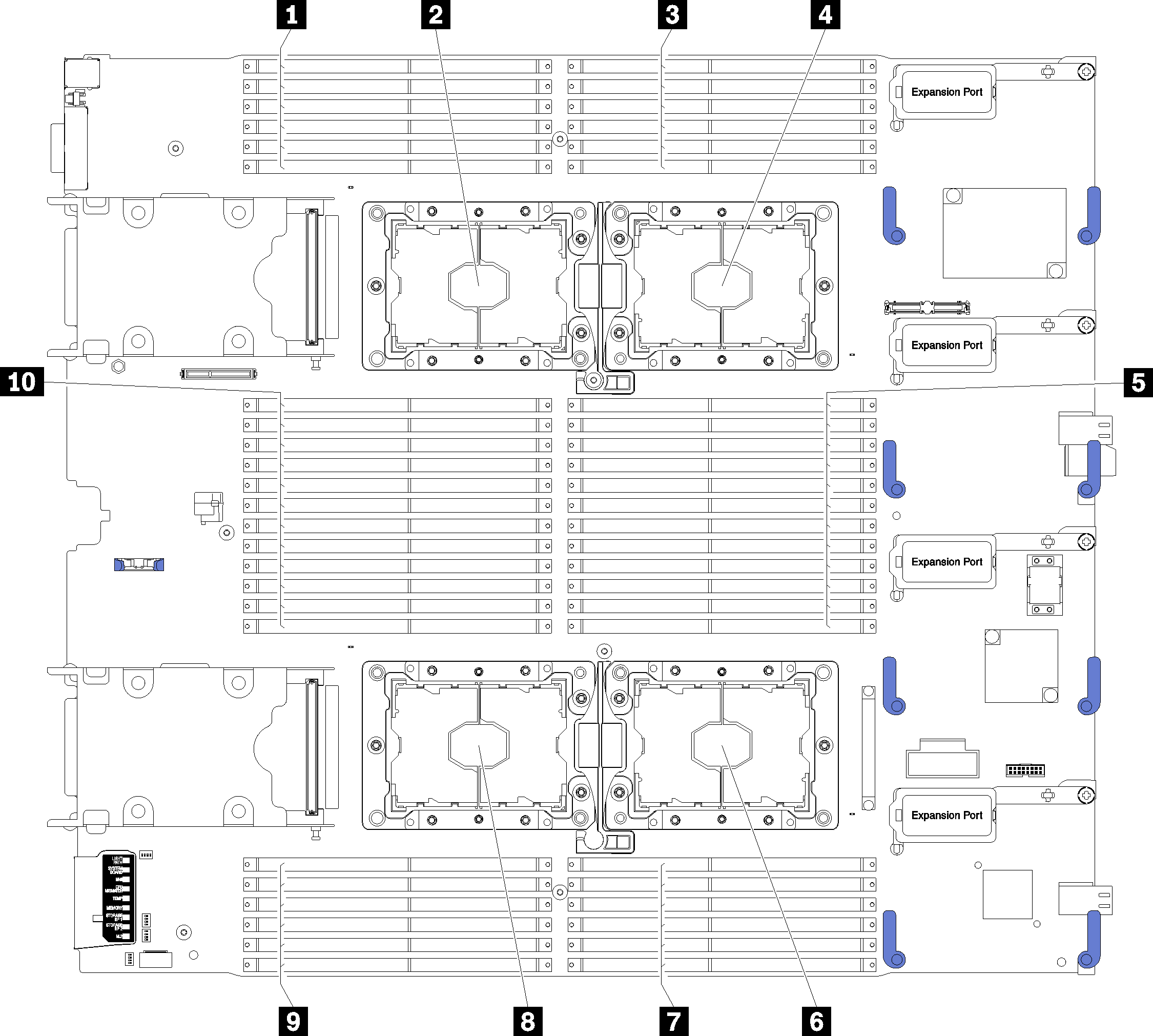

| 1 DIMM 25–30 | 6 Prozessorsockel 2 |

| 2 Prozessorsockel 3 | 7 DIMM 19–24 |

| 3 DIMM 1‑6 | 8 Prozessorsockel 4 |

| 4 Prozessorsockel 1 | 9 DIMM 43‑48 |

| 5 DIMM 7‑18 | 10 DIMM 31‑42 |

| Speichercontroller | Controller 0 | Controller 1 | |||||||||||

| Kanäle | Kanal 2 | Kanal 1 | Kanal 0 | Kanal 0 | Kanal 1 | Kanal 2 | |||||||

| Steckplätze | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 0 | 1 | 0 | |

| DIMM-Nummern (Prozessor 1) | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | |

| DIMM-Nummern (Prozessor 2) | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | |

| Speichercontroller | Controller 1 | Controller 0 | |||||||||||

| Kanäle | Kanal 2 | Kanal 1 | Kanal 0 | Kanal 0 | Kanal 1 | Kanal 2 | |||||||

| Steckplätze | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 0 | 1 | 0 | |

| DIMM-Nummern (Prozessor 3) | 25 | 26 | 27 | 28 | 29 | 30 | 31 | 32 | 33 | 34 | 35 | 36 | |

| DIMM-Nummern (Prozessor 4) | 37 | 38 | 39 | 40 | 41 | 42 | 43 | 44 | 45 | 46 | 47 | 48 | |

Die Speicherspiegelung reduziert den maximal verfügbaren Speicher auf die Hälfte des installierten Speichers. Wenn im Rechenknoten z. B. 64 GB Speicher installiert sind, sind bei Verwendung der Speicherspiegelung nur 32 GB Speicher adressierbar.

DIMMs werden für jeden Prozessor paarweise installiert. Jedes DIMM eines Paares muss die identische Größe und Architektur besitzen.

DIMMs auf den einzelnen Speicherkanälen müssen die gleiche Dichte haben.

Wenn zwei Speicherkanäle über DIMMs verfügen, erfolgt das Spiegeln über zwei DIMMs (Kanäle 0/1 enthalten beide die primären/sekundären Speichercaches).

Wenn drei Speicherkanäle über DIMMs verfügen, erfolgt das Spiegeln über alle drei DIMMs (Kanäle 0/1, Kanäle 1/2 und Kanäle 2/0 enthalten alle die primären/sekundären Speichercaches).

Die DIMM-Belegungsreihenfolgen für die Speicherspiegelung für sämtliche unterstützten Prozessorkonfigurationen werden in einem der folgenden Abschnitte gezeigt: