Espelhamento de Memória

O modo de espelhamento de memória fornece redundância de memória integral ao mesmo tempo que reduz a capacidade de memória total do sistema pela metade. Os canais de memória são agrupados em pares com cada canal que recebe os mesmos dados. Se ocorrer uma falha, o controlador de memória comutará dos DIMMs no canal principal para os DIMMs no canal de backup. A ordem de instalação de DIMMs para o espelhamento de memória varia dependendo do número de processadores e DIMMs instaladas no nó de cálculo.

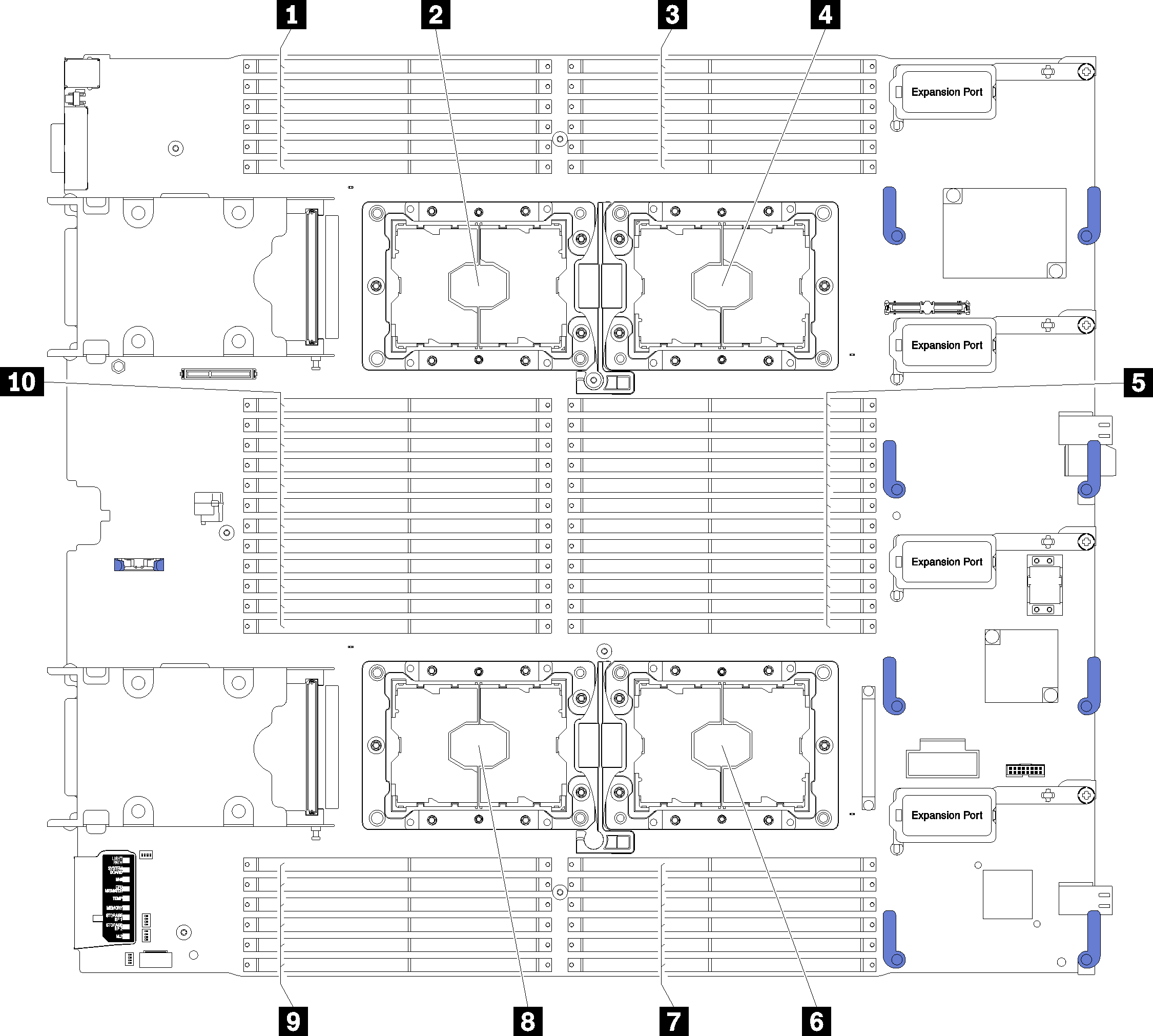

| 1 DIMM 25 – 30 | 6 Soquete de processador 2 |

| 2 Soquete de processador 3 | 7 DIMM 19 – 24 |

| 3 DIMM 1 – 6 | 8 Soquete de processador 4 |

| 4 Soquete de processador 1 | 9 DIMM 43 – 48 |

| 5 DIMM 7 – 18 | 10 DIMM 31 – 42 |

| Controladores de memória | Controlador 0 | Controlador 1 | |||||||||||

| Canais | Canal 2 | Canal 1 | Canal 0 | Canal 0 | Canal 1 | Canal 2 | |||||||

| Slots | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 0 | 1 | 0 | |

| Número de DIMMs (processador 1) | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | |

| Número de DIMMs (processador 2) | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | |

| Controladores de memória | Controlador 1 | Controlador 0 | |||||||||||

| Canais | Canal 2 | Canal 1 | Canal 0 | Canal 0 | Canal 1 | Canal 2 | |||||||

| Slots | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 0 | 1 | 0 | |

| Número de DIMMs (processador 3) | 25 | 26 | 27 | 28 | 29 | 30 | 31 | 32 | 33 | 34 | 35 | 36 | |

| Número de DIMMs (processador 4) | 37 | 38 | 39 | 40 | 41 | 42 | 43 | 44 | 45 | 46 | 47 | 48 | |

O espelhamento de memória reduz a memória máxima disponível pela metade da memória instalada. Por exemplo, se o nó de cálculo tiver 64 GB de memória instalada, apenas 32 GB de memória endereçável estarão disponíveis quando o espelhamento de memória será ativado.

DIMMs instaladas em pares para cada processador. Cada DIMM de um par deve ser idêntico em tamanho e arquitetura.

As DIMMs em cada canal de memória devem ser iguais em densidade.

Se dois canais de memória tiverem DIMMs, o espelhamento ocorrerá em duas DIMMs (os canais 0/1 conterão os caches de memória primário e secundário).

Se três canais de memória tiverem DIMMs, o espelhamento ocorrerá nas três DIMMs (os canais 0/1, 1/2 e 2/0 conterão caches de memória primário e secundário).

A sequência de preenchimento de DIMMs de espelhamento de memória para cada uma das configurações suportadas do processador é mostrada em um dos seguintes tópicos: