Memory mirroring

Memory-mirroring mode provides full memory redundancy while reducing the total system memory capacity in half. Memory channels are grouped in pairs with each channel receiving the same data. If a failure occurs, the memory controller switches from the DIMMs on the primary channel to the DIMMs on the backup channel. The DIMM installation order for memory mirroring varies based on the number of processors and DIMMs installed in the compute node.

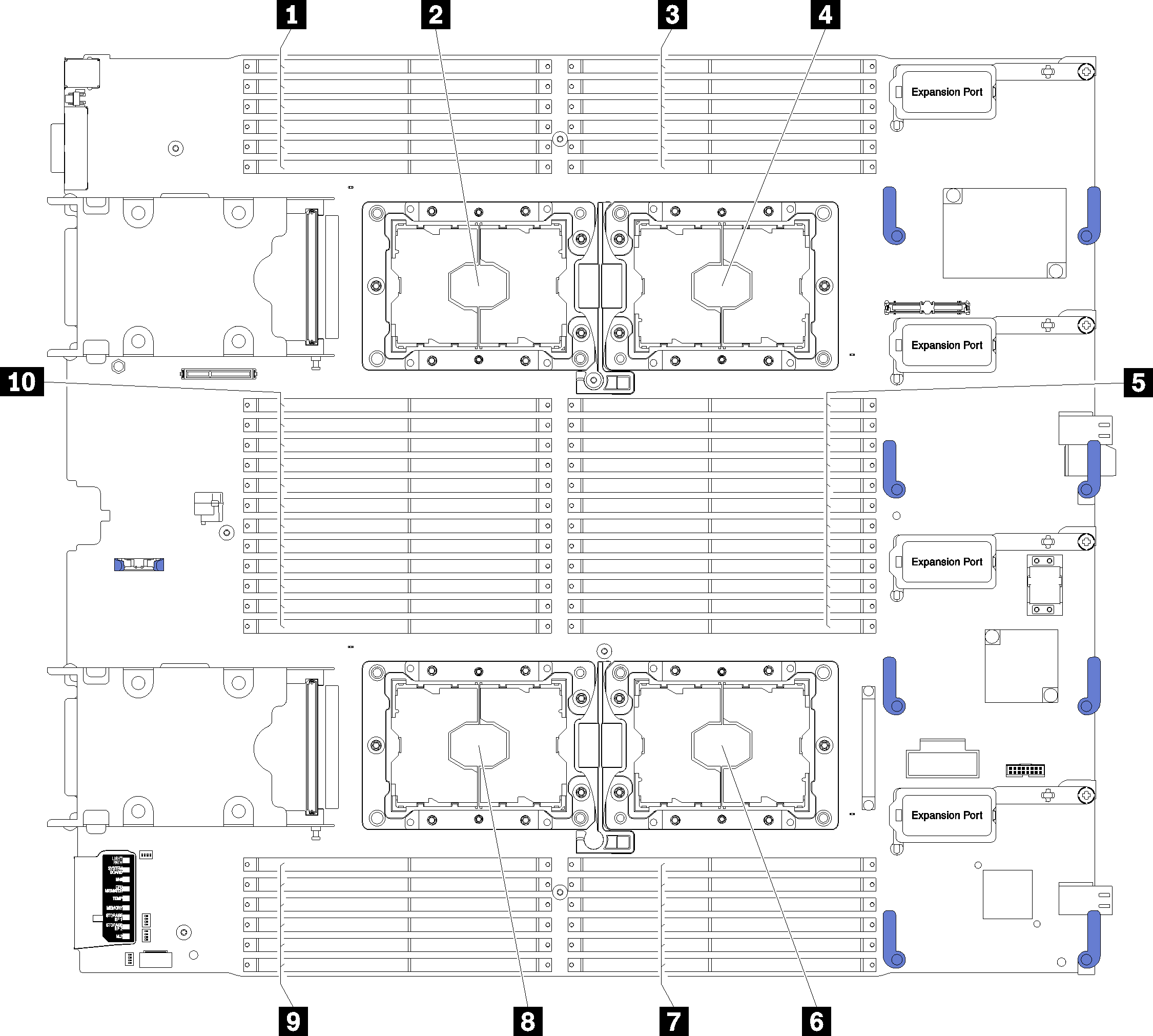

| 1 DIMM 25 – 30 | 6 Processor socket 2 |

| 2 Processor socket 3 | 7 DIMM 19 – 24 |

| 3 DIMM 1 – 6 | 8 Processor socket 4 |

| 4 Processor socket 1 | 9 DIMM 43 – 48 |

| 5 DIMM 7 – 18 | 10 DIMM 31 – 42 |

| Memory controllers | Controller 0 | Controller 1 | |||||||||||

| Channels | Channel 2 | Channel 1 | Channel 0 | Channel 0 | Channel 1 | Channel 2 | |||||||

| Slots | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 0 | 1 | 0 | |

| DIMM numbers (processor 1) | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | |

| DIMM numbers (processor 2) | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | |

| Memory controllers | Controller 1 | Controller 0 | |||||||||||

| Channels | Channel 2 | Channel 1 | Channel 0 | Channel 0 | Channel 1 | Channel 2 | |||||||

| Slots | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 0 | 1 | 0 | |

| DIMM numbers (processor 3) | 25 | 26 | 27 | 28 | 29 | 30 | 31 | 32 | 33 | 34 | 35 | 36 | |

| DIMM numbers (processor 4) | 37 | 38 | 39 | 40 | 41 | 42 | 43 | 44 | 45 | 46 | 47 | 48 | |

Memory mirroring reduces the maximum available memory by half of the installed memory. For example, if the compute node has 64 GB of installed memory, only 32 GB of addressable memory is available when memory mirroring is enabled.

DIMMS are installed in pairs for each processor. Each DIMM in a pair must be identical in size and architecture.

DIMMs on each memory channel must be of equal density.

If two memory channels have DIMMs, mirroring occurs across two DIMMs (channels 0/1 will both contain the primary/secondary memory caches).

If three memory channels have DIMMs, mirroring occurs across all three DIMMs (channels 0/1, channels 1/2, and channels 2/0 will all contain primary/secondary memory caches).

Memory mirroring DIMM population sequences for each of the supported processor configurations is shown by one of the following topics: