Memory sparing

In memory-sparing mode, one memory rank serves as a spare for other ranks on the same channel in case they fail. The spare rank is held in reserve and not used as active memory until a failure is indicated, with reserved capacity subtracted from the total available memory in the system. The DIMM installation order for memory sparing varies based on the number of processors and memory modules installed in the compute node.

After an error threshold is surpassed in a system protected by memory sparing, the content of a failing rank of DIMMs is copied to the spare rank. The failing rank is then taken offline and the spare rank placed online for use as active memory in place of the failed rank. Since the failover process involves copying of memory content, the level of memory redundancy provided by memory sparing is less than that provided by memory mirroring: memory mirroring is the preferred failure-protection choice for critical applications.

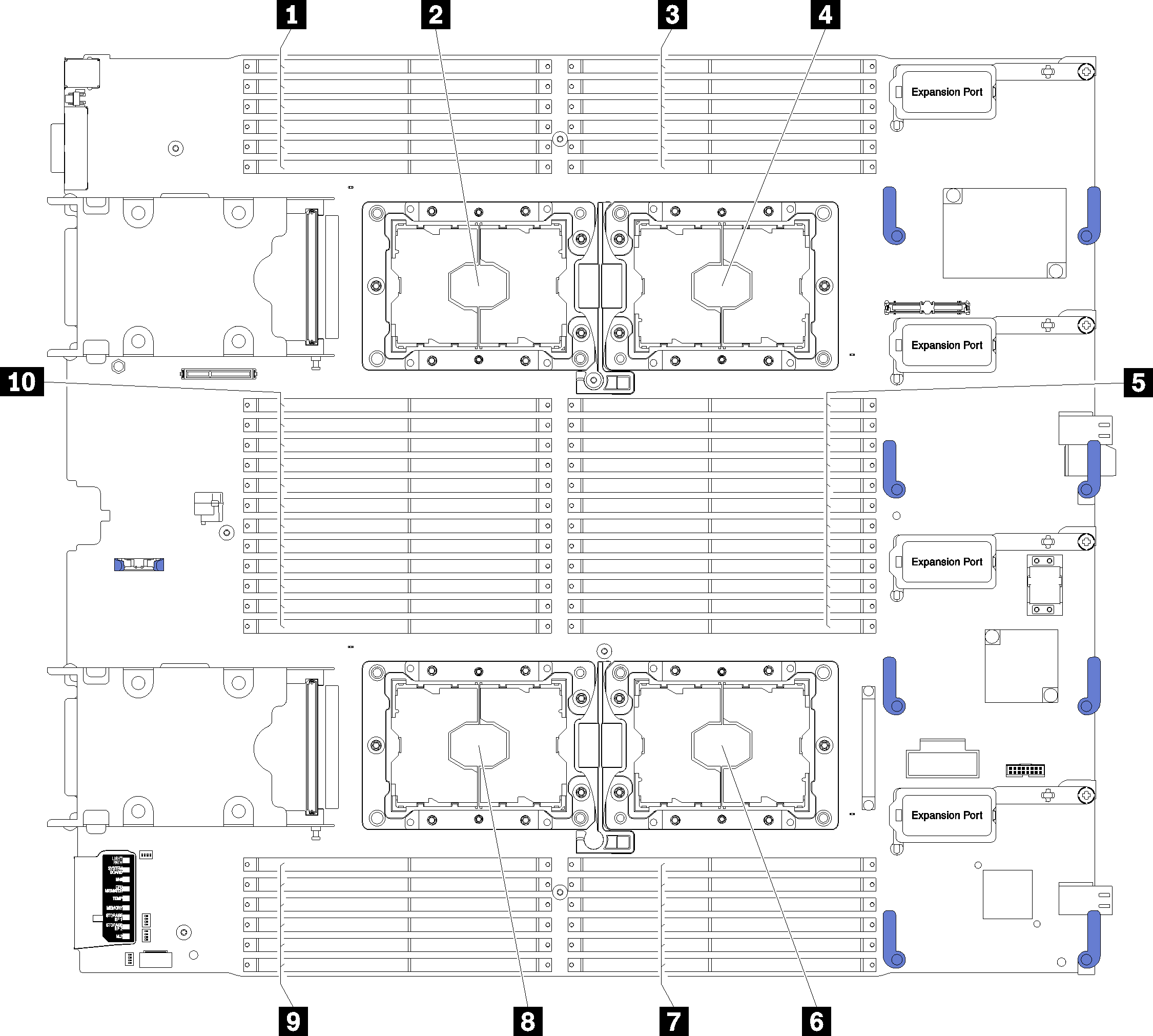

| 1 DIMM 25 – 30 | 6 Processor socket 2 |

| 2 Processor socket 3 | 7 DIMM 19 – 24 |

| 3 DIMM 1 – 6 | 8 Processor socket 4 |

| 4 Processor socket 1 | 9 DIMM 43 – 48 |

| 5 DIMM 7 – 18 | 10 DIMM 31 – 42 |

| Memory controllers | Controller 0 | Controller 1 | |||||||||||

| Channels | Channel 2 | Channel 1 | Channel 0 | Channel 0 | Channel 1 | Channel 2 | |||||||

| Slots | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 0 | 1 | 0 | |

| DIMM numbers (processor 1) | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | |

| DIMM numbers (processor 2) | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | |

| Memory controllers | Controller 1 | Controller 0 | |||||||||||

| Channels | Channel 2 | Channel 1 | Channel 0 | Channel 0 | Channel 1 | Channel 2 | |||||||

| Slots | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 0 | 1 | 0 | |

| DIMM numbers (processor 3) | 25 | 26 | 27 | 28 | 29 | 30 | 31 | 32 | 33 | 34 | 35 | 36 | |

| DIMM numbers (processor 4) | 37 | 38 | 39 | 40 | 41 | 42 | 43 | 44 | 45 | 46 | 47 | 48 | |

The spare rank must have identical or larger memory capacity than all of the other active memory ranks on the same channel.

If installing DIMMs that are one rank, follow the population sequences listed below.

If installing DIMMs with more than one rank, follow population sequences specified for independent memory mode. See Independent memory mode.