Economie de mémoire

En mode de mise en réserve de mémoire, un rang de mémoire sert de secours pour les autres rangs du même canal en cas de défaillance. Le rang de secours est gardé en réserve et n'est pas utilisé comme mémoire active tant qu'aucune défaillance n'est signalée ; la capacité réservée étant soustraite de la quantité totale de mémoire disponible dans le système. L'ordre d'installation des barrettes DIMM pour la mise en réserve mémoire varie en fonction du nombre de processeurs et de modules de mémoire installés sur le nœud de traitement.

Lorsqu'un seuil d'erreur est dépassé dans un système protégé par une mise en réserve mémoire, le contenu d'un rang défaillant des barrettes DIMM est copié dans le rang de réserve. Le rang défectueux est alors mis hors ligne, et le rang de réserve est placé en ligne et utilisé comme mémoire active à la place du rang défectueux. Puisque le processus de basculement implique de copier du contenu de mémoire, le niveau de redondance de la mémoire fourni par cette fonction est inférieur à celui fourni par la mise en miroir mémoire : la mise en miroir mémoire est l'option à préférer pour la protection des applications critiques en cas de défaillance.

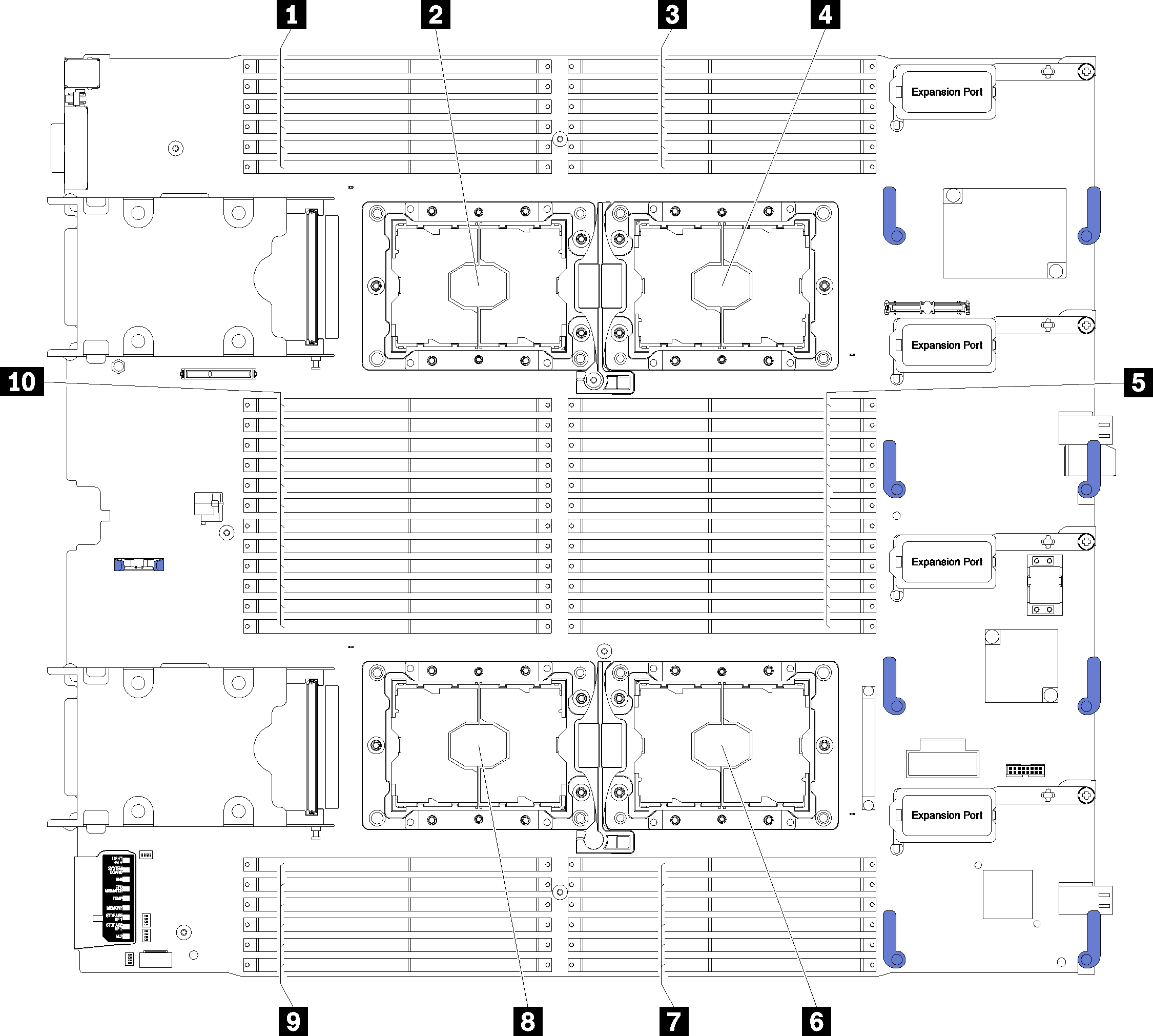

| 1 Barrettes DIMM 25 – 30 | 6 Connecteur de processeur 2 |

| 2 Connecteur de processeur 3 | 7 Barrettes DIMM 19 – 24 |

| 3 Barrettes DIMM 1 – 6 | 8 Connecteur de processeur 4 |

| 4 Connecteur de processeur 1 | 9 Barrettes DIMM 43 – 48 |

| 5 Barrettes DIMM 7 – 18 | 10 Barrettes DIMM 31 – 42 |

| Contrôleurs de mémoire | Contrôleur 0 | Contrôleur 1 | |||||||||||

| Canaux | Canal 2 | Canal 1 | Canal 0 | Canal 0 | Canal 1 | Canal 2 | |||||||

| Emplacements | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 0 | 1 | 0 | |

| Numéros de barrette DIMM (processeur 1) | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | |

| Numéros de barrette DIMM (processeur 2) | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | |

| Contrôleurs de mémoire | Contrôleur 1 | Contrôleur 0 | |||||||||||

| Canaux | Canal 2 | Canal 1 | Canal 0 | Canal 0 | Canal 1 | Canal 2 | |||||||

| Emplacements | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 0 | 1 | 0 | |

| Numéros de barrette DIMM (processeur 3) | 25 | 26 | 27 | 28 | 29 | 30 | 31 | 32 | 33 | 34 | 35 | 36 | |

| Numéros de barrette DIMM (processeur 4) | 37 | 38 | 39 | 40 | 41 | 42 | 43 | 44 | 45 | 46 | 47 | 48 | |

La capacité de mémoire du rang de réserve doit être identique ou supérieure à celles de tous les autres rangs de mémoire active sur le même canal.

Si vous installez des barrettes DIMM qui constituent un seul rang, suivez les séquences de remplissage indiquées ci-après.

Si vous installez des barrettes DIMM qui constituent plusieurs rangs, suivez les séquences de remplissage indiquées pour le mode mémoire indépendant. Pour plus d'informations, voir Mode mémoire indépendant.