Mise en miroir de la mémoire

Le mode de mise en miroir fournit une redondance de la mémoire tout en réduisant de moitié la capacité de mémoire de tout le système. Les canaux de mémoire sont regroupés par paires et chaque canal reçoit les mêmes données. Si une panne se produit, le contrôleur de mémoire passe des barrettes DIMM situées sur le premier canal à celles du canal de sauvegarde. L'ordre d'installation des barrettes DIMM en mise en miroir de la mémoire varie en fonction du nombre de processeurs et de barrettes DIMM installé sur le nœud de traitement.

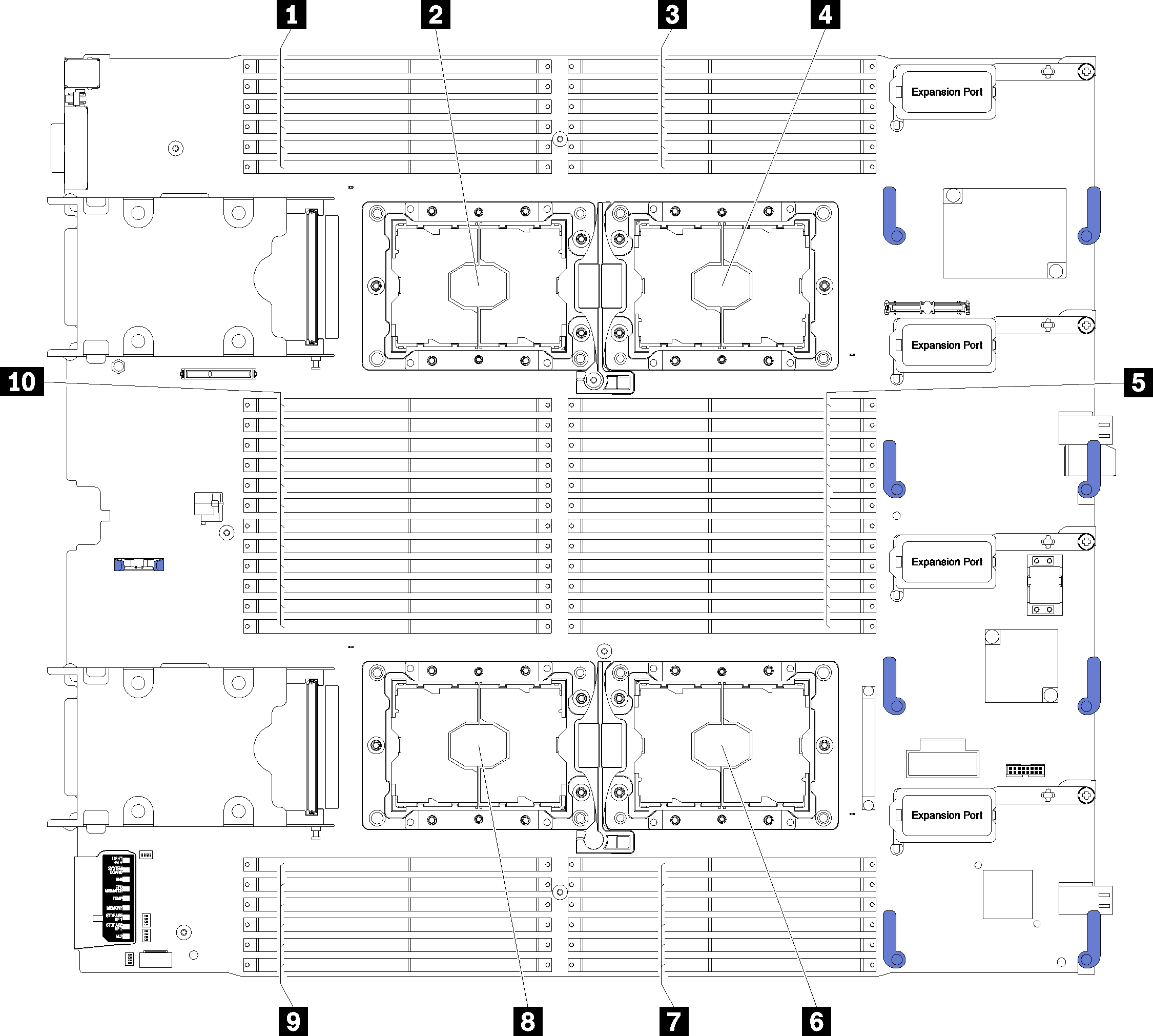

| 1 Barrettes DIMM 25 – 30 | 6 Connecteur de processeur 2 |

| 2 Connecteur de processeur 3 | 7 Barrettes DIMM 19 – 24 |

| 3 Barrettes DIMM 1 – 6 | 8 Connecteur de processeur 4 |

| 4 Connecteur de processeur 1 | 9 Barrettes DIMM 43 – 48 |

| 5 Barrettes DIMM 7 – 18 | 10 Barrettes DIMM 31 – 42 |

| Contrôleurs de mémoire | Contrôleur 0 | Contrôleur 1 | |||||||||||

| Canaux | Canal 2 | Canal 1 | Canal 0 | Canal 0 | Canal 1 | Canal 2 | |||||||

| Emplacements | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 0 | 1 | 0 | |

| Numéros de barrette DIMM (processeur 1) | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | |

| Numéros de barrette DIMM (processeur 2) | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | |

| Contrôleurs de mémoire | Contrôleur 1 | Contrôleur 0 | |||||||||||

| Canaux | Canal 2 | Canal 1 | Canal 0 | Canal 0 | Canal 1 | Canal 2 | |||||||

| Emplacements | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 0 | 1 | 0 | |

| Numéros de barrette DIMM (processeur 3) | 25 | 26 | 27 | 28 | 29 | 30 | 31 | 32 | 33 | 34 | 35 | 36 | |

| Numéros de barrette DIMM (processeur 4) | 37 | 38 | 39 | 40 | 41 | 42 | 43 | 44 | 45 | 46 | 47 | 48 | |

La mise en miroir mémoire réduit de moitié la quantité disponible maximum de la mémoire installée. Par exemple, si le nœud de traitement dispose d'une mémoire installée de 64 Go, il ne reste que 32 Go de mémoire adressable si la mise en miroir est activée.

Les barrettes DIMM sont installées par paires pour chaque processeur. La taille et l'architecture de chacune des barrettes DIMM d'une paire doivent être identiques.

Les barrettes DIMM de chaque canal de mémoire doivent être de densité égale.

Si deux canaux de mémoire possèdent des barrettes DIMM, la mise en miroir se produit sur deux barrettes DIMM (les canaux 0/1 contiennent tous les deux les caches principaux ou secondaires de la mémoire).

Si trois canaux de mémoire possèdent des barrettes DIMM, la mise en miroir se produit sur les trois barrettes DIMM (les canaux 0/1, les canaux 1/2 et les canaux 2/0 contiennent tous les caches principaux ou secondaires de la mémoire).

Les séquences de remplissage de barrettes DIMM en miroir pour chaque configuration de processeur prise en charge sont indiquées par l'une des rubriques suivantes :