システム・ボード・アセンブリーのスイッチ

このセクションでは、システム I/O ボードとプロセッサー・ボードが搭載されたシステム・ボード・アセンブリーのスイッチ・ブロックの位置と機能について説明します。

重要

スイッチの設定を変更する、あるいはジャンパーを移動する前には、サーバーの電源をオフにしてください。次に、すべての電源コードおよび外部ケーブルを切り離してください。以下の情報を確認します。

- このドキュメントの図に記載されていないシステム・ボード・アセンブリーのスイッチまたはジャンパー・ブロックは、予備です。

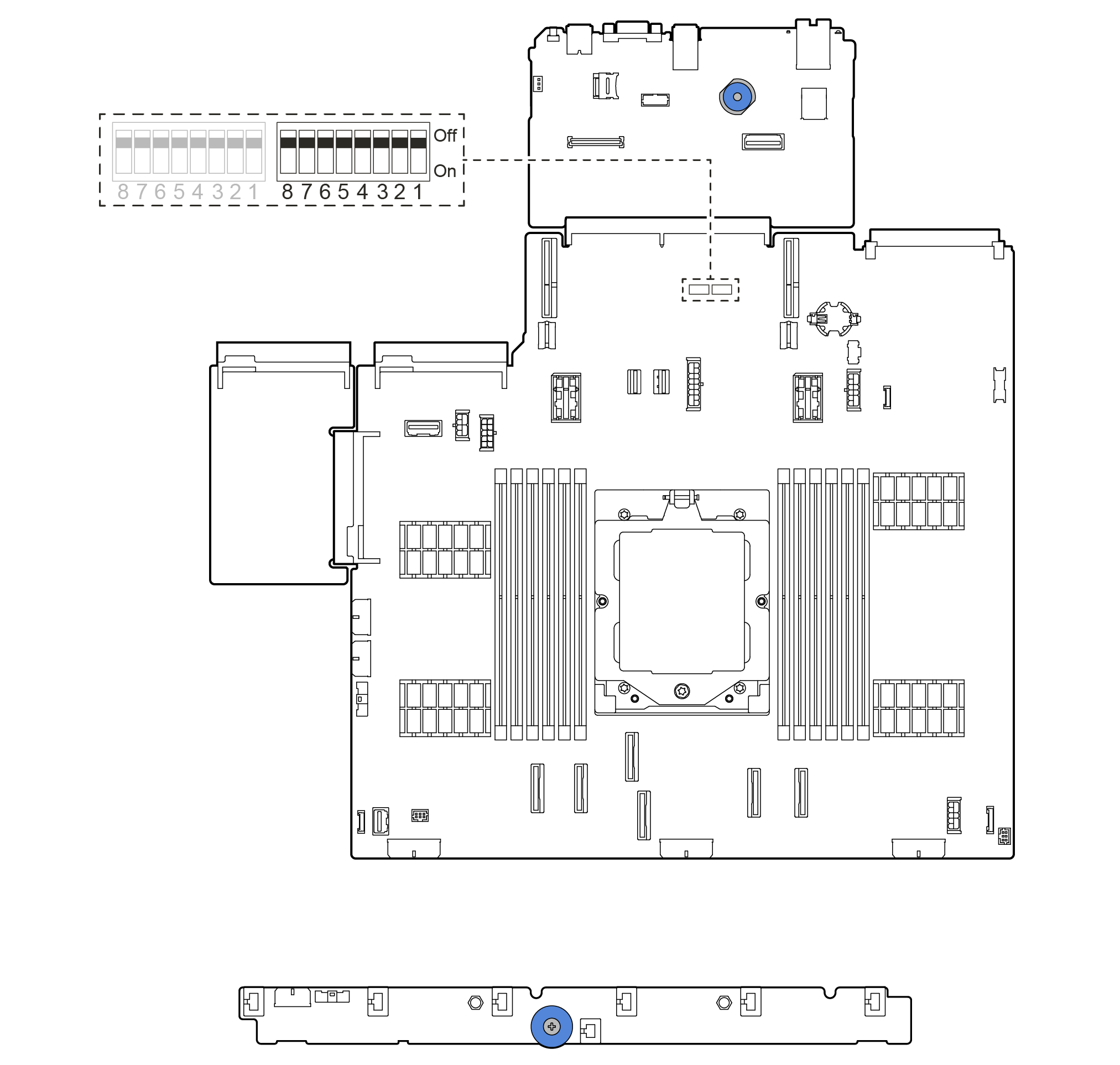

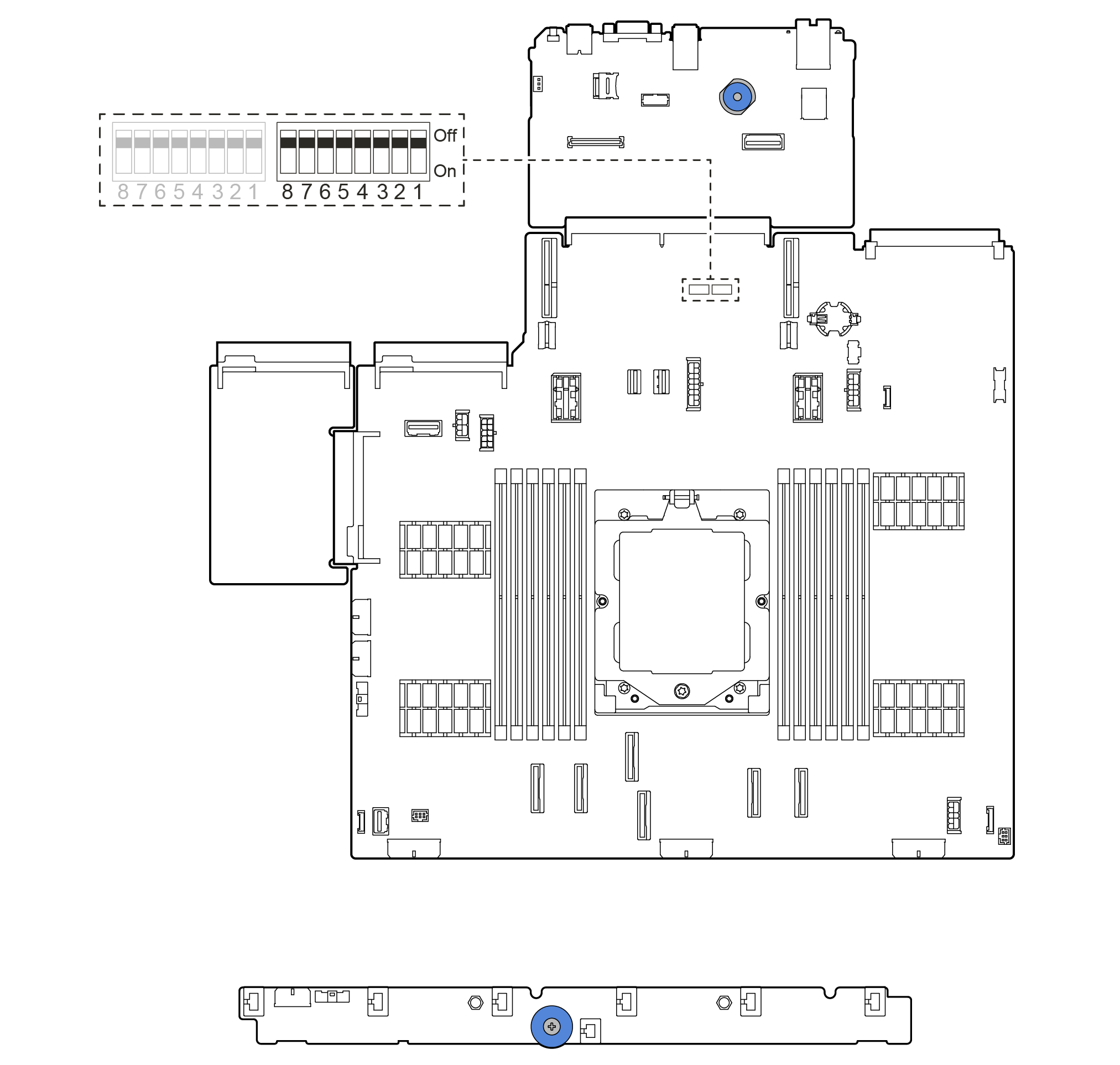

図 1. システム・ボード・アセンブリー上のスイッチ・ブロック

SW5 スイッチ ・ブロック

以下の表は、システム・ボード・アセンブリー上にある SW5 スイッチ・ブロックについて説明しています。

| スイッチ番号 | スイッチ名 | デフォルト位置 | 説明 |

|---|---|---|---|

| SW5-1 | BMC CPU リセットの強制 | オフ | オン位置に変更すると、BMC と CPU が強制的にリセットされます。 |

| SW5-2 | CMOS クリア | オフ | オン位置に変更すると、リアルタイム・クロック (RTC) レジストリーがクリアされます。 |

| SW5-3 | 始動パスワードのオーバーライド | オフ | オン位置に変更すると、始動パスワードがオーバーライドされます。 |

| SW5-4 | FPGA のリセット | オフ | オン位置に変更すると、FPGA が強制的にリセットされます。 |

| SW5-5 | 予約済み | オフ | 予約済み |

| SW5-6 | 予約済み | オフ | 予約済み |

| SW5-7 | 予約済み | オフ | 予約済み |

| SW5-8 | 予約済み | オフ | 予約済み |

フィードバックを送る